作者: 团子

审核专家: 彭练矛,北京大学信息学院“博雅”特聘教授、纳米器件物理与化学教育部重点实验室主任

如今,人们的生活已经离不开智能手机。去年发布的iphoneXS手机容量最大可配置为512GB,而十年前8GB就已经能称得上手机存储的顶级配置了。短短十年, 手机存储几十倍的增长正是集成电路高速发展的产物。此外,手机运行速度的加快、电脑尺寸的减小、存储容量和主频的增加等均与集成电路的发展息息相关 。

集成电路的最小功能单位为晶体管,配合一些被动元器件(如:电阻)可实现不同的功能。衡量集成电路的重要指标之一为集成度————单位面积的芯片上可容纳的晶体管数量。

(目前,人们的生活已经离不开手机。图片来源:Pixabay)

摩尔定律说,集成电路中晶体管的数量每两年增长一倍。这条定律准确地预测了半导体行业的高速发展。在摩尔定律的指导下,过去的半个世纪里,硅基集成电路的制造工艺一直稳步向前演进,半导体产业在历经了上世纪六十年代的IC(集成电路)时代,八十年代的VLSI(超大集成电路)时代,发展到当下的Gb、Tb时代。而在未来较长的一段时间内,硅基集成电路依旧是半导体技术的主流。

近二十年来,晶体管的技术节点不断缩小:130 nm、90 nm、 65 nm、 45 nm、 32 nm、 22 nm,14 nm,7 nm(当下最先进的制程),5/3 nm(研发中)。随着技术节点的缩小,硅基芯片的集成度越来越高(即单位面积的晶体管数量的增加),随之而来的是容量更大的存储以及更快的计算速度。然而,不容忽视的一点是,高集成度带来的功耗问题会影响芯片的工作可靠性以及晶体管的性能。 因而,集成电路产业的主要目标已经由最初的提升性能和集成度转变为降低功耗。

减小晶体管功耗最有效的方法是降低工作电压(VDD)和提高晶体管开关态转换速率。目前所使用的传统硅基互补金属氧化物半导体集成电路(14/10 nm技术节点)的VDD和SS值的极限值分别为0.64V和60mV/DEC(毫伏/量级电压与开关转换速率已达到了极限。新型微电子器件中能满足小工作压电和低亚阈值摆幅的有隧穿场效应晶体管、碰撞电离场效应晶体管和负电容场效应晶体管等。但这些晶体管有着速度低、稳定性差等重要缺陷。

在国家重点研发计划“纳米科技”重点专项的支持下,北京大学信息科学技术学院物理电子学研究所、纳米器件物理与化学教育部重点实验室张志勇教授、彭练矛教授课题组提出一种 新型超低功耗的场效应晶体管 —— 狄拉克源场效应晶体管 (DS-FET)。

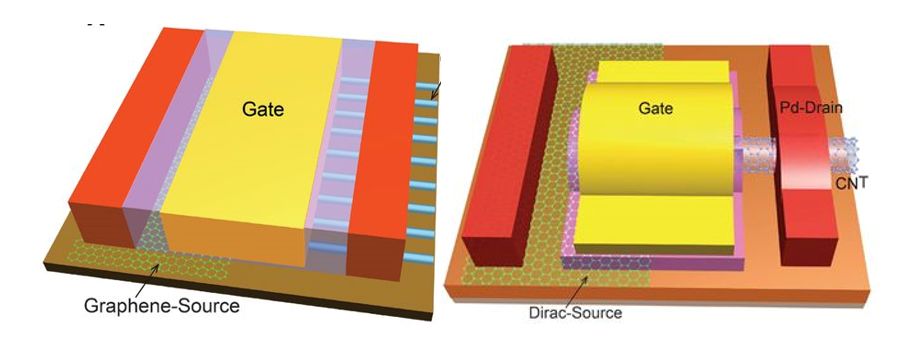

这种新型晶体管通过三个部分以下三个方面的调控调制沟道电学特性提高了性能:把晶体管比作一个电路,那么掺杂石墨烯就是“电源”掺杂石墨烯为冷电子源,碳纳米管即为“导线”为有源沟道,高效率顶栅结构而电路的开关在此种新型结构中效率也更高。多批器件测试结果显示狄拉克晶体管的性能突破了传统晶体管的极限值。并且当狄拉克晶体管的尺寸进一步缩小时,性能依旧稳定。且开态电流高于10微安,可与目前报道的性能最好的p型碳纳米管场效应管相媲美。 DS-FET不仅满足超低功耗的要求还具有良好的可缩减性,完全达到了国际半导体发展路线图的标准,极有希望成为将来亚0.5V集成电路的基础元件。

狄拉克源晶体管的提出突破了传统互补金属氧化物半导体的亚阈值摆幅极限值60mV/DEC,在沟道缩短的情况下,性能依旧可观。用作“导线”的材料除碳纳米管外,石墨烯狄拉克源也可与还有多种其它半导体沟道材料选择(如:尺寸在半导体纳米级别的线状结构、二维半导体材料或者传统半导体材料等)相结合,这种灵活性与可兼容性为研发低功耗高性能晶体管提供了多种可能性,也为3nm以后技术节点的集成电路技术提供多种解决方案。

超低功耗集成电路晶体管介绍:

排版:凝音

题图来源:Pixabay

科普中国公众号

科普中国公众号

科普中国微博

科普中国微博

帮助

帮助