摩尔定律即将失效?实则正以3D芯片形式延续,通过垂直堆叠突破物理极限,实现性能跃升与成本优化。芯片架构革命如何推动未来计算?

(本图片由图虫创意提供,仅供于科普中国平台使用)

从体积巨大的古董电脑,再到如今非常小巧的笔记本电脑以及手机,计算设备的进化史堪称是一场奇迹,而这场奇迹的核心驱动力是一个我们耳熟能详的名字——摩尔定律。

摩尔定律并非是物理定律,而是英特尔创始人之一戈登·摩尔在1965年提出的一个产业预言和经济学目标。他观察到,大约每18到24个月,同样面积的芯片上可以容纳的晶体管数量会增加一倍,成本也会下降。

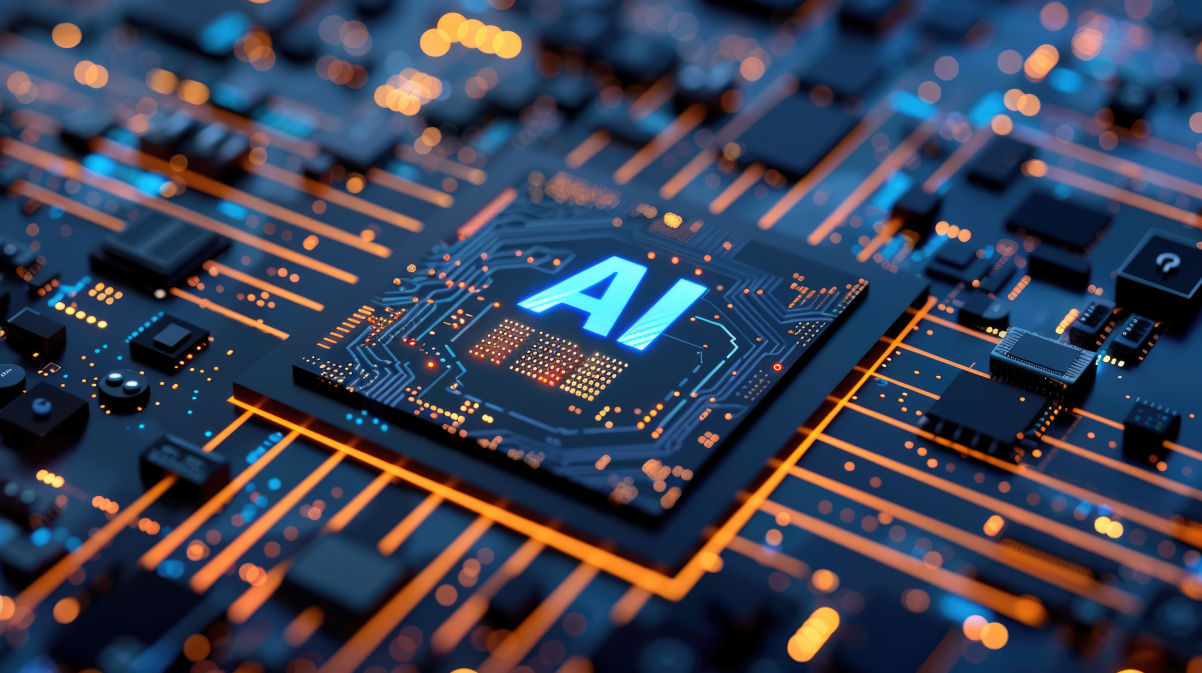

在过去的几十年里,整个行业都在遵循摩尔定律这个路线图疯狂地奔跑。晶体管做的越来越小,从微米级到纳米级,就像把一座城市里的道路和建筑不断去微缩,从而在同一块地里去塞进了更多的东西。这带来了一个非常非常大的感受是什么呢?手机性能越来越强,电脑越来越快,但是价格却越来越亲民。

芯片加工(本图片由图虫创意提供,仅供于科普中国平台使用)

不过,任何狂奔都是会有终点的,当晶体管的尺寸逼近几个纳米的物理极限时,科学家们遇到了大麻烦。

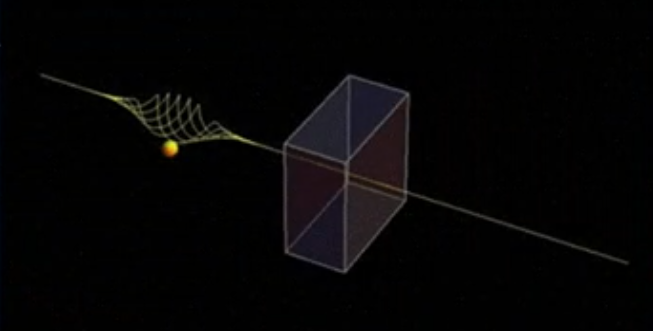

第一个麻烦是量子隧穿效应。晶体管内部的绝缘层如果薄到了几个原子的厚度,电子就会像有了穿墙术一样漏过去,这会导致芯片发生错误,功耗也会飙升。

量子隧穿效应

第二个危机是极端发热问题。大家可以想象一下,数十亿个晶体管挤在纳米尺度的空间内,它的功率密度堪比火箭发动机的喷口。

第三个困难是经济成本。建造一座生产最先进的制成芯片的工厂,它的成本高达数百亿美金,这些成本最终都会转嫁到每一颗芯片上。摩尔定律所说的“成本会下降”这部分预言好像逐渐变得不那么真实了。

所以说,摩尔定律是要失效了吗?

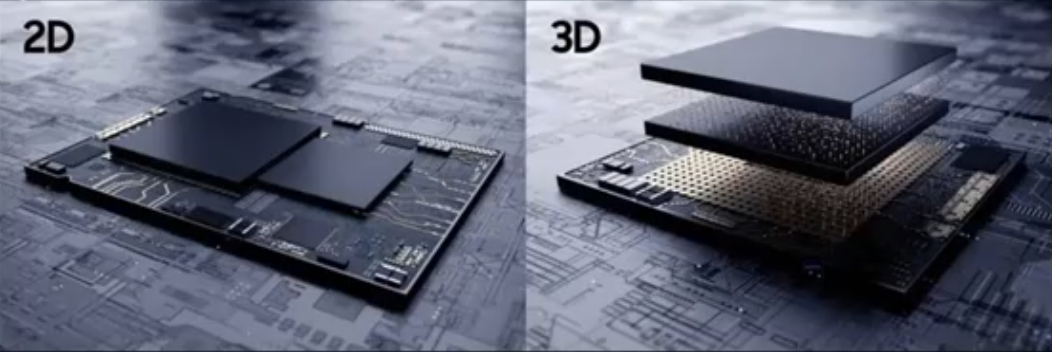

最近几年大家发现,与其说失效,不如说它正在换一种方式延续。当平面微缩这条技术路线越走越窄的时候,科学家们发挥了一个非常朴素的智慧:既然平面铺不开了,那就向上发展,建高楼,这就是3D芯片技术。

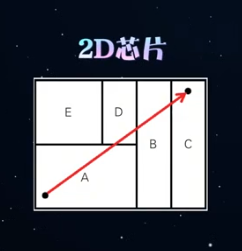

传统的芯片是一个平房村落,所有的晶体管都铺在同一侧,信号要穿过漫长而拥挤的街道才能到它另一端,既慢又非常耗电。而3D芯片是一个摩天大楼,科学家们通过先进的封装技术将多个计算芯片、内存芯片,甚至不同工艺的芯片,像搭积木一样垂直堆叠在一起,并且通过3D互联的技术设计层与层之间的高速电梯,从而将它们纵向紧密连接。

我们可以想象一下,在新的3D芯片里,计算单元之间不再是隔着一个城市的“远房表亲”,而是住在上下楼的邻居,数据交换的距离降低了几个数量级,信号传输的速度得到了极大的提升,功耗也显著降低。

通过严谨的实验数据对比和分析可以看到,3D IC可以提供更小的面积、更多的内部连接、更低的功耗。

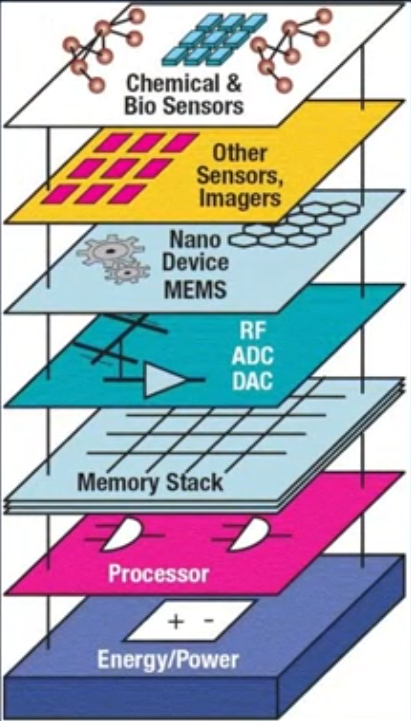

3D IC带来了另外一个革命性优势,叫异质集成。我们可以不必再用最昂贵、最先进的工艺来生产所有的东西,比如说我们可以让CPU用5纳米工艺,内存用更成熟的工艺,模拟芯片用另外一种特色工艺,然后把它堆叠到一颗芯片里。在3D的架构中,让专业的芯片干专业的事,最终实现最佳的性能和成本的均衡。

异质集成

得益于垂直堆叠架构的优势,3D IC可以提供更高的性能、更低的功耗、更小的面积、更大的存储空间、更高的互联带宽,广泛适用于对性能要求极为苛刻的场景。

虽然说单个平面上的晶体管数量增长放缓,但是通过垂直向上堆叠的3D架构,实现了系统层面的晶体管密度倍增,从而让摩尔定律得以延续。

从摩尔定律的平面微缩到3D芯片的垂直拓展,这标志着集成电路行业从二维时代迈入了三维时代,这不再是一场单纯的微缩竞赛,而是一场关于芯片架构、集成、协同计算更深层次的创新。芯片内部的这场空间革命正悄然塑造了我们更智能更高效的未来。

主讲人:邸志雄 西南交通大学集成电路学科与工程学院副院长

本文为科普中国·创作培育计划扶持作品

作者:中国电子学会

审核:周祖成 清华大学电子工程系 教授

出品:中国科协科普部

监制:中国科学技术出版社有限公司、北京中科星河文化传媒有限公司

来源: 科普中国创作培育计划

来源: 科普中国创作培育计划

内容资源由项目单位提供

科普中国公众号

科普中国公众号

科普中国微博

科普中国微博

帮助

帮助

科普中国创作培育计划

科普中国创作培育计划